# Si/Ge Junctions Formed by Nanomembrane Bonding

Arnold M. Kiefer,<sup>†</sup> Deborah M. Paskiewicz,<sup>†</sup> Anna M. Clausen,<sup>†</sup> Walter R. Buchwald,<sup>‡</sup> Richard A. Soref,<sup>‡</sup> and Max G. Lagally<sup>†,\*</sup>

<sup>+</sup> University of Wisconsin—Madison, Madison, Wisconsin 53706, United States, and <sup>+</sup> Sensors Directorate, Air Force Research Laboratory, Hanscom AFB, Massachusetts 01731, United States

he direct bonding of dissimilar semiconductors provides many opportunities for the design of novel hybrid optoelectronic devices<sup>1-3</sup> and micro- and nanoelectromechanical systems (MEMS and NEMS).<sup>4</sup> The formation of high-quality interfaces and electronic junctions directly between dissimilar materials is, however, significantly constrained by materials properties. In one limit, heteroepitaxy provides the best achievable structural interfaces, but heteroepitaxy can be accomplished only for materials with small differences in lattice constants (and thus in composition), before dislocation formation or total loss of crystalline order results. Only device structures for which such small compositional differences are acceptable are possible, and their properties, in turn, are degraded by dislocation formation. $5^{-7}$  In the alternative, formation of a heterojunction by wafer bonding, thermal-expansion mismatch during bonding or thermal cycling frequently leads to either complete or local bond failure and the generation of massive numbers of dislocations, depending on the materials and the process.8

In particular, the formation of a heterojunction between Si and Ge by growth or wafer bonding has been generally unsuccessful. Such a structure is constrained by a 4.2% mismatch in lattice parameter and a ratio of thermal expansion coefficients of about 2:1 (Ge:Si).<sup>9</sup> Yet, there are many reasons why such junctions would be useful, for example, photovoltaics,<sup>10,11</sup> photodetectors,<sup>12,13</sup> light emitters,<sup>14</sup> and radio frequency MEMS<sup>15</sup> compatible with Si device fabrication technology.

In efforts to circumvent the problems inherent in heteroepitaxy or bulk wafer bonding, we consider here a different approach, the bonding of a free-standing, monocrystalline semiconductor nanomembrane [Si] to a bulk substrate of a dissimilar material [Ge] (or more generally, the bonding of two dissimilar **ABSTRACT** We demonstrate the feasibility of fabricating heterojunctions of semiconductors with high mismatches in lattice constant and coefficient of thermal expansion by employing nanomembrane bonding. We investigate the structure of and electrical transport across the interface of a Si/Ge bilayer formed by direct, low-temperature hydrophobic bonding of a 200 nm thick monocrystalline Si(001) membrane to a bulk Ge(001) wafer. The membrane bond has an extremely high quality, with an interfacial region of  $\sim$ 1 nm. No fracture or delamination is observed for temperature changes greater than 350 °C, despite the approximately 2:1 ratio of thermal-expansion coefficients. Both the Si and the Ge maintain a high degree of crystallinity. The junction is highly conductive. The nonlinear transport behavior is fit with a tunneling model, and the bonding behavior is explained with nanomembrane mechanics.

**KEYWORDS:** nanomembrane  $\cdot$  heterojunction  $\cdot$  bonding  $\cdot$  semiconductor  $\cdot$  silicon  $\cdot$  germanium

nanomembranes to each other). This approach is made possible by the development of methods to release very thin single-crystal sheets (10–500 nm) by etching away a buried layer of different composition using a highly selective chemical etchant and to transfer these sheets to an arbitrary new host substrate (for a review, see ref 16). The ability to bond thin, single-crystal membranes to rigid substrates or to each other at low temperatures provides increased flexibility in the fabrication of hybrid electronic, optoelectronic, and thermoelectric-device structures.

Two important questions immediately arise: (1) How well can one bond dissimilar materials if one or both are nanomembranes? (2) How does the interface between such a bonded pair influence electronic transport across the interface? To address these questions, we bond a very thin (200 nm) sheet of single-crystal Si to a bulk Ge substrate and measure charge transport across the bonded interface.

We find exceedingly good bonding of membranes to a host substrate, with a narrow, well-defined interface. We explain the bonding behavior in terms of elastic properties of thin membranes and strain \* Address correspondence to lagally@engr.wisc.edu.

Received for review November 19, 2010 and accepted January 5, 2011.

Published online January 19, 2011 10.1021/nn103149c © 2011 American Chemical Society

VOL.5 • NO.2 • 1179-1189 • 2011

sharing between thick and thin materials. We demonstrate that the interface is likely due only to twist boundaries. Cross-membrane electrical transport is nonlinear, with a quite high minimum conductance, sufficiently high for practical applications. We fit the interfacial charge transport using a tunneling model.

# **RESULTS AND DISCUSSION**

**Nanomembrane Transfer and Bonding.** Semiconductor nanomembranes (NMs) are rapidly emerging as a new platform technology. The interest has focused on both the fabrication of novel structures<sup>17–19</sup> and the transfer and bonding of membranes to new hosts.<sup>20–22</sup> In these efforts, for a variety of reasons, the detailed structural and electrical quality of the bond interface is not of concern in the science or technology being explored. Here, we are specifically interested in those aspects, as our goal is to investigate the extent to which a semiconductor NM bond interface can produce high cross-interface electrical conductance.

We fabricate silicon nanomembranes from commercially available Soitec Smart Cut silicon-on-insulator (SOI) substrates. The silicon template layer is patterned using standard optical lithography to define membranes and to create access channels to the buried oxide layer. The patterned SOI is submerged in a solution of hydrofluoric acid to etch away the buried oxide layer and release the membrane from the thick handle substrate. We form bonded junctions between Si and Ge by transferring an ~200 nm thick Si(001) NM to a bulk Ge(001) substrate by either a wet- or a dry-transfer technique and annealing the composite system at a temperature of 400 °C with no applied external pressure. Both the Si NM and the Ge surfaces are chemically etched prior to bonding.

In a wet-transfer process, the NM is always kept in water or dilute HF etching solution. Because its surface is hydrophobic under these conditions, the NM floats on the solution surface. Surface tension keeps the NM flat but applies negligible stress that, if it were large, could damage extremely thin (<100 nm) membranes during manipulation. The membrane is moved to the host substrate in liquid or the host substrate is dipped into the liquid containing the membrane to initiate contact and bonding.

Alternatively, for relatively thick NMs (>100 nm), a temporary adhesive stamp may be used for simultaneous dry transfer of large areas or patterns of membranes. We use thermal-release tape in this transfer method. After the membranes are released by etching away the oxide, they are allowed to settle back onto the original substrate (the handle wafer in SOI). The NMs, which are now only weakly bonded to the substrate by van der Waals forces, are simply picked up using the thermal-release tape and transferred to the new host substrate. Heating the substrate and tape together causes the tape adhesive to foam,

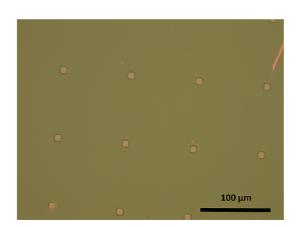

Figure 1. Optical micrograph of a 220 nm thick Si NM bonded to a bulk Ge substrate and annealed at 400  $^\circ$ C. The membrane was transferred using thermal-release tape. The lighter areas are holes in the NM for etchant access to the originally underlying silicon dioxide.

reducing the contact area and adhesion with the membrane. The tape is lifted off, leaving the membranes on the new substrate. Residual adhesive is chemically removed. An example of a transferred NM is shown in Figure 1.

To increase adhesion and promote covalent bonding between the membrane and the new host material, the Si NM—Ge pair is heated slowly from 100 to 400 °C at a rate of 5 °C/min, held at 400 °C for 30 min, and ramped down to 50 °C at the same rate. Using optical microscopy, we observe no fracture, buckling, or delamination of the Si NM throughout the annealing process. Widely separated bubbles occasionally form, presumably due to trapped gases or particle contamination. These areas do not affect the overall membrane bonding quality and cause no extended-defect formation.

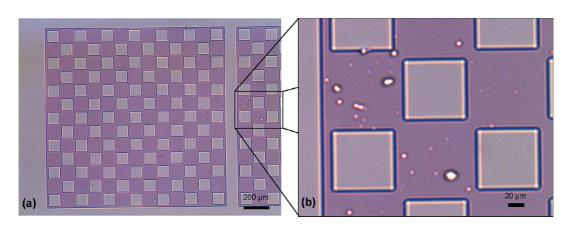

Figure 2 demonstrates some of the features of a transferred and annealed Si/Ge bonded pair. Si NMs, each 1.32 mm square, are prepared from SOI via lithographic patterning and released. Several such NMs were transferred simultaneously in registry to a Ge wafer using thermal-release tape. Figure 2 shows one complete checkerboard and part of an adjacent one. In the right checkerboard in the image, particles contaminating the Ge surface before bonding allow us to show how limited their effect is. The exceptionally low bending stiffness of NMs means that they are so compliant that they simply wrap around these very occasionally occurring particles. Although particles at the interface are clearly not desirable, their presence is not catastrophic and their impact is localized. For wafer bonding or Smart Cut transfer, these particles would have created very large unbonded areas.<sup>8</sup>

The success of nanomembrane bonding, relative to bulk wafer bonding, is explained as follows. First, the thinness of the membrane results in an extremely conformal film on the microscale, increasing the initial contact area and, therefore, total adhesion energy. Second, for a thin film on a relatively thick, rigid substrate,

VOL.5 • NO.2 • 1179-1189 • 2011

Figure 2. Optical micrographs of Si NM/Ge bonded pairs. (a) 220 nm thick Si(001) NMs prepared with large square holes in a checkerboard pattern are transferred to a Ge(001) substrate using thermal-release tape and bonded at 400 °C. Si is dark, and the Ge is seen through the holes as light areas. The holes are 80  $\mu$ m  $\times$  80  $\mu$ m. The size of a complete membrane is 1.32 mm  $\times$  1.32 mm. One complete membrane and part of another are shown. (b) A magnified view of the outlined area on the left shows particles trapped at the interface with the Si NM tightly enclosing them.

essentially all of the thermal-mismatch strain energy resides in the thin film.<sup>23</sup> The amount of strain energy stored in the film is directly proportional to its thickness. When very thin compared to the substrate, the bonded membrane contains insufficient strain energy to drive separation or cause fracture. The calculated maximum in-plane strain in a 220 nm Si NM bonded to Ge for annealing to 400 °C is only 0.12%, with a corresponding in-plane stress of 0.22 MPa. The film simply stretches in plane with the Ge substrate, and negligible bending of the substrate occurs.

We contrast this result to typical wafer bonding of smooth wafers of thermally mismatched materials, where each wafer is of the order of a few hundred micrometers thick.<sup>24</sup> In such a configuration, the outof-plane bending stress caused by unequal expansion is borne by both wafers. This stress drives crack propagation from the edges of the wafer either through the bulk of a wafer or at the bonding interface. Under conditions of initially strong interfacial adhesion or externally applied pressure, some of the strain may be relaxed by microcracks, dislocations, or phase transformations at the interface. These defects are avoided in nanomembrane bonding by remaining below the critical stress—or equivalently, the critical thickness of the membrane for the onset of these failure mechanisms.<sup>23</sup>

The transfer of free-standing nanomembranes is qualitatively different from the Smart Cut (*i.e.*, ion-cutting) process of transferring thin layers to a new host substrate on the wafer scale.<sup>25</sup> In the Smart Cut process, the transferred layer is rigidly affixed to either the source wafer or the new host wafer at all times. The bonding surfaces must be extremely flat and smooth on all length scales and particle-free to ensure good initial adhesion, because of the rigidness of the wafers. Otherwise, large areas remain unbonded with significant residual stress near encapsulated particles or surface asperities. In contrast, a free-standing membrane

is able to stretch and bend. Membranes can conform more readily to surface asperities and may be bonded to nonplanar surfaces. Furthermore, membrane transfer and bonding avoids the polishing and etching needed in Smart Cut transfers to remove damage from the thin-film exfoliation process. The additional polishing step usually requires thicker films to be transferred, thus limiting the transferred film's compliancy during the bonding step.

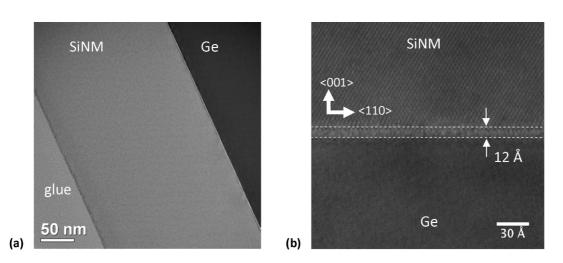

Interface Quality. The above optical-microscopy results suggest excellent interface quality after bonding the Si NM to the bulk Ge. We investigate the interfaces and the crystallographic integrity of the bond in greater detail with cross-sectional transmission electron microscopy (XTEM). Figure 3 shows a high-resolution XTEM micrograph of the interface of a Si(001) NM/Ge(001) bonded pair fabricated by dry transfer. The lower-magnification image (Figure 3a) shows that the Si NM/Ge bond interface has no inhomogeneities: extended defects, inhomogeneous strain fields, precipitates, and inclusions are absent from the bond interface and in the crystalline material near the interfacial region. Figure 3b is a highresolution image of the interfacial region between the Si and Ge. The XTEM samples were fabricated such that the [110] direction of the Si NM is perpendicular to the face of the cross-section. When bonding the Si NM to the Ge, there is typically a twist angle  $(\theta)$  between similar in-plane directions of the NM and the substrate. We determine this twist angle to be  $\sim$ 22° by measuring the tilt angle between the [110] directions in the Si NM and the Ge substrate with transmission electron diffraction (see the Materials and Methods section). Lattice fringes are visible in the Si NM, indicating that the NM remains crystalline throughout the bonding process. The high twist bond angle, between the Si NM and the Ge substrate, prevents the appearance of high-resolution fringes from the Ge substrate in the same image as the Si. Nevertheless, electron diffraction patterns of the Ge very near the interfacial region indicate that the Ge is

VOL.5 • NO.2 • 1179-1189 • 2011

Figure 3. Transmission electron microscopy images of the interface region between a Si(001) NM bonded to a Ge(001) substrate by dry transfer and annealed at 400 °C. (a) XTEM image showing the entire thickness of the Si NM with no strain variations or extended defects near the interface. (b) A high-resolution image oriented along the Si(110) zone axis. The crystalline orientation of the Si NM is as shown. The interfacial region is  $\sim$ 1.2 nm thick.

monocrystalline. The interfacial region appears to be amorphous and approximately 1.2 nm thick.

To place our results in context, we summarize here the experimental evidence and simulation of interfaces of bonded bicrystals that has emerged in recent years. Several experimental studies of single-element hydrophobic (*i.e.*, hydrogen-terminated) bonding of Si(001)/ Si(001) wafers indicate that the interfacial structures fall into three categories with respect to twist angle  $(\theta)$ .<sup>26</sup> If  $\theta < 5^{\circ}$ , the interface is crystalline with a network of dislocations at the interface; for  $5^{\circ} < \theta < 10^{\circ}$ , the interface is partly crystalline with amorphous regions forming at the interface; and for  $\theta > 10^{\circ}$ , the interface is entirely amorphous. No lattice constant mismatch (only orientation changes) is involved.

In general, a crystalline interface can be described within the standard framework of bicrystallography.<sup>27</sup> At low twist angles, the underlying symmetry of the crystal structure is preserved at the interface because of the high density of coincident-lattice sites of the joined crystals. It is energetically favorable to form patches of a continuous crystal across the interface with an array of screw dislocations bounding the crystalline regions to produce the lowest interfacial energy. The distance between dislocations (*S*<sub>d</sub>) for these particular crystal structures is given by<sup>28</sup>

$$S_{\rm d} = \frac{a_1 a_2}{[2(a_1^2 + a_2^2 - 2a_1 a_2 \cos \theta)]^{1/2}}$$

(1)

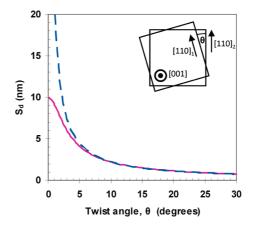

where  $a_1$  and  $a_2$  are lattice constants of the two crystals and  $\theta$  is the twist angle between the lattice vectors within the interfacial plane. A plot of the dislocation spacing as a function of twist angle is shown in Figure 4. For simplicity, we ignore the slight tilt misorientation from the ideal (001) surface planes, which also produces interfacial defects.

For the Si(001)/Ge(001) interface, the dislocations require an edge component to account for the 4.2%

Figure 4. Plot of eq 1 showing the dislocation spacing  $(S_d)$  as a function of twist angle using parameters for a Si(001)/Si(001) interface (dashed line) and a Si(001)/Ge(001) interface (solid line). There is little difference above 5°. For Si/Si,  $S_d$  asymptotically approaches infinity as  $\theta$  approaches 0.

lattice mismatch. The dislocation spacing with no twist is 10 nm and is completely edge-type in character. With an increase in twist angle, the dislocations have both screw and edge components. As can be seen from Figure 4, the dislocation spacing at the Si/Ge interface converges to that of the Si/Si interface for  $\theta > 5^{\circ}$ . Because of their similar crystal structures and sp<sup>3</sup> bonding nature, we assume that Si/Ge high-angle twist boundaries will be similar in character to Si/Si high-angle twist boundaries. For high twist angles, the density of coincidentlattice sites is very low, resulting in a very small spacing between screw dislocations. Organization of the interface into crystalline regions is no longer energetically favorable. The interfacial atoms instead rearrange into an amorphous layer to bond the two surfaces covalently while maintaining the highly directional sp<sup>3</sup> bonds.

Molecular dynamics simulations of high-angle twist boundaries formed between grains of nanocrystalline Si show that an amorphous interlayer exists between

VOL. 5 • NO. 2 • 1179-1189 • 2011

grains.<sup>29</sup> The calculated radial density function for these interlayers is practically identical to that of bulk amorphous Si. The principal conclusion of these simulations is that the amorphous interlayer is energetically lower than alternative interfaces, making it the thermodynamically preferred state for twist angles greater than 10°. Otsuki measured the interfacial energy between Si(001) twist boundaries from  $0^{\circ}$  to  $45^{\circ}$  and found that the interfacial energy for twist angles >10° was nearly constant, in agreement with the simulations.<sup>30</sup> The simulations also predict that the interlayer tends to be between 4 and 8 ML (monolayers) thick, independent of twist angle. The vast majority of Si atoms within the amorphous layer is 4-fold coordinated with less than 10% of them either 3- or 5-fold coordinated, indicating that the density of dangling bonds near the interface is less extensive than one may initially expect. The low stiffness of NMs makes it likely that the interface region is as least as small, and possibly smaller, than for bulk crystals.

Thus far, we have only considered geometrical relationships for predicting the structure of the interface. Si and Ge constitute a fully miscible binary alloy system, and interdiffusion could, in principle, drive morphological changes of the interface. Interdiffusion is, however, unlikely to be significant at the temperatures and times used in our experiments. As an example, the diffusivity of Si in Ge is on the order of  $10^{19}$  cm<sup>2</sup>/s at 550 °C.<sup>31</sup> Assuming the same diffusivity at a much lower 400 °C, the diffusion length is on the order of 1 Å in 30 min. Although the more open structure of the interface may enhance diffusion, diffusion beyond the interfacial layer is negligible.

Additionally, interfacial contamination could, in principle, play a role. Because our surfaces are hydrophobic, we can rule out most contamination possibilities, even though the initial contact between our bonded surfaces occurs in an ambient atmosphere. Hydrophobic bonding generally produces thinner interfacial lavers or crystalline interfaces with minimal extrinsic defects.<sup>32</sup> However, hydrophobic surfaces in bulk wafer bonding generally produce interfaces with low adhesive energy and require higher annealing temperatures to create strong interfacial bonding. For fullwafer bonding, thermal-expansion mismatch limits annealing temperatures to values below those necessary to form sufficiently strong interfaces. In contrast, NMs are ultracompliant and are able to maximize the contact area with the host substrate and to stretch without creation of defects at higher thermal-mismatch strain. Consequently, the benefits of hydrophobic bonding are available to NM bonding. Any lowtemperature bonding scheme employing hydrophilic or plasma treated surfaces will likely produce wider interfaces, due to incorporation of other elements.<sup>33,34</sup> The measured interfacial conductivity of bonded hydrophobic Si/Si wafers is clearly superior to hydrophilic bonding for this reason.<sup>32</sup> If electrical conduction across the interface is desired, hydrophilic bonding, even though it is much easier in bulk materials, is counterproductive. As we demonstrate here with NMs, hydrophobic bonding produces excellent interfaces.

We conclude that the bonded Si/Ge interface structure is a thin amorphous layer created by twist boundaries. This interfacial region is thermodynamically stable and only a few lattice constants wide, owing to the strong sp<sup>3</sup> bonding, which drives atomic reorganization at the interface. Interdiffusion will be insignificant for the range of temperatures and times under consideration. Because our Ge and Si NMs are hydrogenterminated, contamination is minimal and does not likely contribute to the interface width.

**Electrical Characterization.** Membrane bonding in the manner described above creates a narrow interfacial region with a high density of atomic defects. Simplistically, any interface creates a barrier to charge transport. In principle, the interface can always be made more resistive by deliberately adding an interfacial dielectric layer. We attempt to minimize the dielectric layer to make the cross-barrier conductivity high, and our narrower interface, relative to conventional wafer bonding of Si and Ge, presents that opportunity.<sup>33,34</sup>

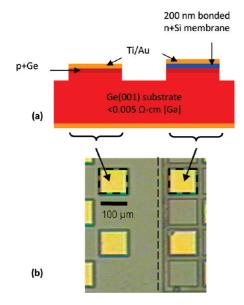

To investigate cross-interface conduction, we use a 200 nm n<sup>+</sup>–Si NM (4  $\times$  10<sup>20</sup>/cm<sup>3</sup>) bonded to a p<sup>+</sup>–Ge wafer (>1  $\times$  10<sup>20</sup>/cm<sup>3</sup>) and annealed at 400 °C for 30 min (see the Materials and Methods section). High doping reduces depletion regions, thus better defining the interface electrically, and ensures a high density of mobile carriers for enhanced charge transport.

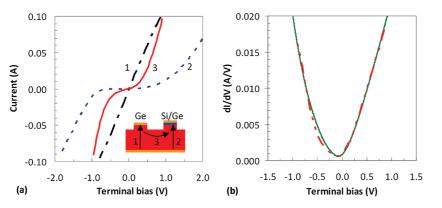

After transferring the Si NM, we create 100  $\mu$ m  $\times$  100  $\mu$ m mesas of Ge and Si/Ge and deposit metal contacts, as depicted in Figure 5. Current–voltage (*I*–*V*) characteristics are then measured from mesa to mesa. Positive bias is defined with respect to the Si contact as ground. Typical results of dc *I*–*V* measurements are shown in Figure 6a. The maximum relative errors were 0.3% for current and 0.01% for voltage at zero applied bias with no dependence on the polarity of the swept voltage. There was no appreciable difference in curves from pads measured at adjacent sites.

We confirmed that Si contacts were Ohmic on separate control devices formed using the same SOI substrate from which the Si NMs were fabricated. dc current—voltage measurements of bonded Si/Ge interfaces are shown in Figure 6a for three different current paths defined in the inset. Path 1 is from a bottom contact on the Ge bulk substrate to a Ge mesa contact on the top; the curve confirms Ohmic conduction through the bulk Ge wafer and Ge contacts. Path 2 is from the bottom Ge contact to a Si/Ge mesa contact on the top; at high biases, the current parallels path 1, indicating that conduction has become limited by the series resistance of the bulk substrate. Path 3 is from the top Ge mesa contact to the Si/Ge mesa contact; the

current increases much more rapidly with applied bias as compared to path 2 through the bulk. It is, therefore, clear that series resistance influences the I-V characteristics of the bonded Si/Ge mesa, and we consider the extracted conductance to be a lower limit of the actual conductance of the interface.

We have calculated the conductance from Ge-to-Si/ Ge mesa charge transport measurements by taking the derivative of the I-V curve of path 3 in Figure 6a and compared it to the measured conductance of the same device path using an ac impedance meter (Figure 6b). The ac conductance measured at different junction biases and fixed frequency (10 kHz) matches the conductance calculated from the dc I-V measurements

Figure 5. Device structures for cross-interface charge transport measurements. (a) A schematic diagram of a cross section of a mesa-type Si/Ge diode (right mesa). The mesas are etched  $\sim 2.4 \,\mu$ m below the original Ge surface prior to evaporation of Ti/Au contacts. (b) An optical micrograph of Ge mesas (left) and Si/Ge mesas (right) used for charge transport measurements.

(see the Materials and Methods section ). The minimum specific conductance, defined as the conductance normalized by the total interface area ( $1.0 \times 10^{-4}$  cm<sup>2</sup>), is 6 S/cm<sup>2</sup> at a bias of approximately -70 meV.

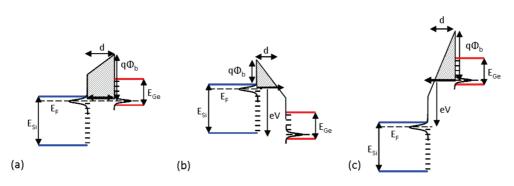

On the basis of structural and electrical observations, we suggest a tunneling model to explain interfacial conductance.<sup>35</sup> The amorphous interfacial layer observed with TEM, even though extremely thin, creates a potential barrier to electronic transport, which may exist in addition to or in place of an interfacial dipole or potential barrier caused by differences in electron affinities and band gaps of the Si and Ge. The barrier must be narrow because we observe high conductance even at low bias.

The device resembles a typical tunneling diode (Figure 7).<sup>36</sup> Both the Si and the Ge are degenerately doped. Degenerate doping creates impurity energy bands within the Si and Ge band gaps that merge with the respective conduction and valence bands. The presence of filled and empty electronic states immediately adjacent to the barrier allows tunneling to occur. However, unlike a tunneling diode, there is no observed negative differential resistance at forward bias when the Fermi level of Si passes through the energy gap of Ge at forward bias. Conduction at this condition is most likely due to the numerous interface states and traps expected to be within the barrier. They provide states within the forbidden band gap by which carriers can tunnel. In addition to trap states, impurity bands can be broad in energy and may provide sufficient overlap of empty and filled states throughout the bandgap region to allow tunneling.

We observe an offset of the conductance minimum to a small negative bias of -70 meV. Such an offset can be explained by a charge imbalance at the interface. The trap states on the silicon (germanium) interface are filled (empty) as a result of the position of the Fermi level at equilibrium (Figure 7a). Accumulation of negative (positive) charge at the Si

Figure 6. Charge transport measurements across bonded NM interfaces of an area of  $100 \,\mu m \times 100 \,\mu m$ . (a) Direct-current I-V measurement made for different current paths: path 1 (black dotted-dashed line), Ge mesa to Ge back contact showing Ohmic behavior; path 2 (blue dashed line), Ge back contact to Si/Ge mesa; and path 3 (red solid line), Ge mesa to Si/Ge mesa. (b) Differential conductance measured with an ac impedance meter (green solid line) is compared to the calculated differential conductance (red dashed-dotted line) from the dc I-V data points measured from path 3 of the Ge mesa to Si/Ge mesa shown in (a).

VOL.5 • NO.2 • 1179-1189 • 2011

Figure 7. Proposed band diagrams for a Si-barrier-Ge tunneling model. The shaded area in each panel represents the effective tunneling barrier, with a width d and height  $q\Phi_b$ . The intrinsic band gaps of Si and Ge are shown, but the Fermi energy,  $E_F$ , passes through the impurity bands. The impurity bands and interface states are represented by curves and dashes, respectively. Tunneling is denoted by a heavy arrow. For clarity, not all tunneling possibilities are shown. At equilibrium (a), tunneling occurs in both directions and no net current is measured (even though the conductance is high). At high forward bias (b), tunneling occurs primarily from the Si conduction band/impurity levels to the Ge conduction band. At high reverse bias (c), tunneling occurs primarily from the Ge valence band/impurity levels to the Si conduction band.

(Ge) interface creates an electric field that has the effect of a positive bias. A negative bias is required to compensate this field.

Having assumed a potential barrier at the interface, we can semiquantitatively predict the conductance or I-V characteristics of the junction. Elastic tunneling occurs in both directions simultaneously, producing a net current. The current density J for the arbitrary case is given by<sup>36</sup>

$$J = \frac{q}{4\pi^2 \hbar} \int \int T[F_1(E) - F_2(E)] dk_{\perp}^2 dE$$

(2)

where *T* is the 1-D barrier transmission probability and the *F*'s are the distributions of occupied states on either side of the barrier. The integrals are evaluated over the range of kinetic energies for which the electron's transverse momentum,  $k_{\perp}$  is the same on both sides of the barrier. Implicit in this formulation is the energy momentum relationship, which must be specified.

The barrier transmission probability is approximated using the Wentzel-Kramers-Brillouin (WKB) approximation

$$T \simeq \exp\left(-\frac{2}{\hbar}\int_{0}^{d}|k(x)|dx\right)$$

(3)

where k is the wave vector of the electron within the barrier and the integration limits are the classical turning points at the barrier's edges. For a rectangular barrier of height  $q\Phi_{\rm b}$  and width d, the transmission probability is approximately

$$T \simeq \exp(-\alpha d\sqrt{\Phi_{\rm b}})$$

(4)

where  $\alpha = 2(2qm^*)^{1/2}/\hbar$  and  $m^*$  is the effective mass within the barrier. It is clear from this expression that a change in barrier width has a greater influence on the transmission probability than a change in barrier height.

The minimum transmission probability occurs when the product  $d(\Phi_b)^{1/2}$  is greatest; that is, the barrier is

approximately rectangular. An applied voltage distorts the barrier and changes its transmission probability. At low biases, the barrier is trapezoidal. The width remains essentially constant, and the barrier height effectively changes. At high biases, the barrier becomes triangular and the tunneling distance changes linearly with the applied voltage. This is the classical Fowler–Nordheim (FN) tunneling regime often observed in metal–insulator– metal or metal–insulator–semiconductor devices. The current density is given by the expression<sup>36</sup>

$$J = \frac{q^2 V^2}{16\pi^2 \hbar d^2 \Phi_{\rm b}} \exp\left(\frac{-4\sqrt{2qm^*} d\Phi_{\rm b}^{3/2}}{3\hbar V}\right)$$

(5)

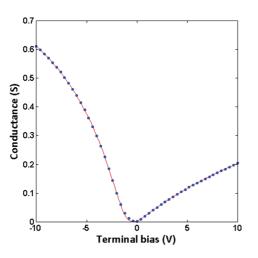

At high applied bias, the current density increases approximately as the square of the voltage drop and not exponentially as for a typical p-n junction. The change in conductance is then approximately linear with increasing voltage. Figure 8 is a plot of conductance measured with an impedance meter from -10 to +10 V of terminal bias. The conductance follows the functional form of a Fowler–Nordheim tunneling model for both forward and reverse biases. The deviation from linearity results from a constant series resistance (0.73  $\Omega$ ) that was included in the calculation. For low biases (|V| < 1 V), the measured conductance deviates slightly from the FN model because the barrier width is essentially fixed and direct tunneling through a trapezoidal barrier occurs.

The observed asymmetry of the conductance results from an asymmetric energy barrier with respect to Si and Ge. The height of the barrier on the incident (transmitted) side is determined by the energy of the filled (empty) state. An applied bias not only distorts the barrier (Figure 7b, c) but also changes the state to which the carrier tunnels. For example, in reverse bias, the Fermi level of Si moves below that of Ge, bringing an empty state higher in the Si conduction band to the same energy as the filled state in the Ge valence band. Thus, reverse bias reduces the effective barrier height,

Figure 8. ac conductance as a function of terminal bias. The data (blue dots) are fit applying only a Fowler–Nordheim tunneling model (red solid line) assuming a barrier width of 1.2 nm and a series resistance of 0.73  $\Omega$ . In forward bias,  $\Phi_{\rm b}$  = 1.27 eV and  $m^*$  = 0.0170  $m_{\rm e}$ ; in reverse bias,  $\Phi_{\rm b}$  = 1.94 eV and  $m^*$  = 0.8354  $m_{\rm e}$ .

increasing the tunneling probability. Other factors that may affect asymmetry in conductance include the effective masses of carriers, the dielectric constants, and the density of states of the Si, Ge, and interfacial layer.

A tunneling model can explain the trends in interfacial conductance by correlating current with barrier transmission probability, and a numerical fit can yield physically reasonable parameters. However, the fit is not unique based solely on these data because of the mathematical interdependencies of the parameters within the model. A precise, quantitative extraction of interfacial properties from modeling requires extreme caution for several reasons: (1) Our simplified model does not explicitly address the different band structures of Si and Ge. As both are indirect-gap semiconductors, inelastic processes are required to conserve momentum during tunneling. This added constraint should dramatically reduce the tunneling current. (2) Knowledge of the distribution of the interface states, both spatially and energetically, is presently inadequate to estimate their role quantitatively in conduction. We expect  $\sim 10^{13}/\text{cm}^2$  unsatisfied or strained Si bonds at the interface because Si has a higher planar density of atoms than Ge. This high number of states in combination with the high degree of atomic disorder within the barrier makes it unlikely that a single, uniform barrier potential will apply across the entire interface. A small fractional change in barrier width locally can cause dramatic changes in current density, making homogeneous current flow across the interface unlikely. (3) The effective mass of carriers within the barrier is unknown. It has been shown that energy-momentum dispersion relations of a disordered barrier cannot be accurately determined solely by analysis of conductance curves.<sup>37</sup>

Because of the general overwhelming difficulty in forming bonded Si/Ge structures, measurements of electrical transport across bonded Si/Ge interfaces to compare to ours are scarce. The difference in interface structural and chemical quality makes a quantitative comparison futile in any case. However, as an example, Zahler *et al.* employed a  $p^+$ –Ge layer bonded to a p<sup>+</sup>-Si substrate and report an interfacial resistance of 400  $\Omega$  cm<sup>2,11</sup> By comparison, the resistance of our bonded n<sup>+</sup>-Si NM/p<sup>+</sup>-Ge junction is significantly less,  $< 1 \Omega$  cm<sup>2</sup>, of considerable value for high-current-density applications, such as photovoltaics, where high interfacial conductance is crucially important to reduce resistive losses.<sup>10</sup> In general, we can state that our membrane bonded junction conducts very well, well enough, even without optimization, for many applications that require electronic transport across a bonded heterojunction. Thus, nanomembrane bonding can serve as the basis of optoelectronic devices, such as a Si/Ge tandem solar cell, a Si/Ge/Si PIN photodetector, or Si/ Ge light emitters.

We have not so far attempted to optimize interfacial conductance. We expect that even higher conductance can be achieved by appropriate surface preparation prior to bonding and by optimizing thermal treatments. Furthermore, postbonding interface modification, such as annealing in forming gas, may lead to a modification of the barrier and thus different I-V characteristics with presumably higher currents.

# CONCLUSIONS

We show successful bonding of a 200 nm thick crystalline Si sheet to a bulk Ge substrate using hydrophobic bonding, characterize the bonding interface, and fabricate diode device structures on this bonded pair to explore cross-interface electrical transport. No indication of separation, fracture, or strain inhomogeneity is observed, demonstrating that NM bonding is an effective and viable method to join highly lattice mismatched materials. XTEM measurements show a very well defined, extremely narrow interface region, controlled by structure rather than interface chemistry, because NM bonding is successful even if hydrophobic surfaces are bonded. Hydrophobic bonding of nanomembranes thus offers a new direction for integration of materials for novel hybrid electronic devices that circumvents the serious problems associated with bulk wafer bonding. Our nanomembrane bonded devices are nonlinear and give a minimum specific conductance of 6 S/cm<sup>2</sup> without any effort at optimization.

Our structural and electronic study of bonded Si/Ge nanomembranes, a material combination that has resisted conventional approaches, makes novel Si/Ge devices that require cross-interface conduction a realistic possibility. More generally, one can expect to extend nanomembrane bonding to other material

VOL.5 • NO.2 • 1179-1189 • 2011

combinations, with similar beneficial outcomes. With the current rapid progress in the manipulation, transfer, and stacking of nanomembranes,<sup>38</sup> the high-quality interfaces obtained in nanomembrane bonding make it likely that a new generation of flexible, high-performance semiconductor devices will be enabled.

## MATERIALS AND METHODS

Membrane Fabrication. Silicon nanomembranes are fabricated from commercially available Soitec Smart Cut silicon-on-insulator (SOI) substrates with a 220 nm Si(001) template layer on 3  $\mu$ m of buried silicon dioxide. Thinner buried oxides may be used. Prior to fabrication, the membranes are ion-implanted and annealed (see below). Annealing reduces the membrane thickness ~20 nm by oxidation. Standard optical lithography is used to define membranes of various lateral sizes and shapes, as well as etchant access holes. Reactive-ion etching using  $SF_6$  or CF<sub>4</sub> + O<sub>2</sub> removes exposed silicon. The photoresist is removed by soaking in acetone for 10 min using ultrasonication or by pressurized spray. The patterned SOI pieces are cleaned using  $H_2SO_4/H_2O_2$  (1:1) solution in a quartz beaker for 5 min and rinsed in flowing deionized water for 5 min. Particles and residual organic contamination are removed by soaking in a mixture of NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O (1:1:5) for 10 min at 80  $\pm$  5 °C and again rinsed in flowing deionized water for 5 min. The pieces are then placed in concentrated HF (49%) in a Teflon beaker to sit undisturbed to release the Si template layer by differential etching of the buried oxide layer. Etching time varies depending on the thickness of the buried oxide and the required etch distance. Typical etching times are 45  $\pm$  10 min for concentrated HF.

Wet-Transfer Technique. Soon after the complete dissolution of the buried oxide layer, Si membranes may float off the substrate and onto the surface of the liquid solution due to their hydrophobic (H-terminated) surfaces. Frequently, they collapse back onto the original handle substrate during the underetching process and remain weakly bonded. Slight agitation may release them into the liquid. The membranes are then picked out of the water either with Teflon tweezers by electrostatic attraction or by use of a small loop of plastic-coated wire (28 gauge). A water film across the loop provides a surface on which the membrane lies. The membrane is then brought into contact with the new host substrate. Alternatively, the new substrate may be dipped into the beaker with the membrane and pulled out, thus drawing the membrane to the surface by capillary forces. The substrate with membrane is then set on a hot plate at ~110 °C for at least 10 min to allow evaporation of water and to increase initial bonding strength. Usually, any wrinkles in the membrane will smooth out as the shifting interface dries. The final placement and orientation of the membrane is difficult to control using this technique.

Dry-Transfer Technique. Nitto Denko Revalpha Thermal Release Tape (No. 3198LS) may be used to transfer nanomembranes of reasonable thickness (~200 nm) and lateral dimensions on the order of millimeters. The membranes are underetched in HF solution and allowed to collapse onto the original handle substrate. The handle with membranes is then removed from the HF solution and slowly dipped into deionized water to remove residual HF. The substrate with membranes is removed from the water. The thermal-release tape is placed directly on top of the membranes without pressing. An adhesion front starting at the point of first contact spontaneously spreads across the tape/ substrate interface. When the membranes are fully adhered, the tape is carefully peeled with minimum bending, to prevent membrane fracture. Frequently, membranes near the initial peeling edge will crack. The tape with membranes is immediately placed on the new substrate without pressing. A slight bending of the tape will usually ensure only one point or line of contact. The adhesion front is allowed to progress spontaneously and often occurs in <10 min for a 1 cm<sup>2</sup> area. The substrate with tape is then placed on a preheated hot plate just above the tape's release temperature ( $\sim$ 100 °C). After the tape debonds, the tape is lifted off the substrate. Removal of residual adhesive using photoresist stripper (e.g., AZ 300T from AZ Electronic Materials) for Ge substrates is possible, and is done before high-temperature annealing. Very thin membranes cannot be transferred using this technique as the membranes conform to the foaming adhesive layer of the tape rather than adhering to the new substrate.

Ion Implantation. Before membrane fabrication, the Si template layer of the SOI is ion-implanted (Core Systems, California) with P (dose is  $1\times 10^{16}/\text{cm}^2$  at an energy of 12 keV with a 7° tilt) and annealed in  $N_2$  at 950 °C for 45 min to achieve a uniform dopant concentration of  $4 \times 10^{20}$ /cm<sup>3</sup> throughout the template layer thickness, as measured by secondary-ion mass spectroscopy (Evans Analytical Group, NJ). Sheet resistance measurements by transfer length and Greek cross methods confirm the expected carrier concentration.<sup>39</sup> The as-received Ge wafers were p-type (Ga) with a resistivity of 0.005  $\Omega \cdot cm$ . We additionally doped the top 50 nm degenerately to >1  $\times$  10<sup>20</sup>/cm<sup>3</sup> with Ga by ion implantation (dose is  $3 \times 10^{15}$ /cm<sup>2</sup> at 40 keV with a 7° tilt). The dopant concentration was also measured by secondaryion mass spectroscopy. Prior to implantation, 10 nm of PECVD SiO<sub>2</sub> is deposited on the Ge surface to ensure shallow implantation. The implanted Ge is annealed in a rapid thermal annealing tool at 600 °C for 1 min.40

**Germanium Preparation.** It is essential that the Ge substrate remain particle-free to avoid trapping particles at the interface. Once diced or cleaved, the brittle edges of germanium become a persistent source of particle contamination, so whole 2 in. wafers are used whenever possible. Just prior to transfer of the nanomembrane, the deposited and native oxides on the Ge are removed in a mixture of HF/HCI/H<sub>2</sub>O (1:1:10).<sup>41,42</sup>

**Thermal Annealing.** Bonded pairs are heated directly on a programmable hot plate or in a convection oven in nitrogen ambient. The temperature is ramped from 100 to 400 °C at a rate of 5 °C/min, held at 400 °C for 30 min, and ramped down to 50 °C at the same rate. No pressure is applied to the sample during the annealing step.

Mesa Device Fabrication. We define  $100\,\mu m \times 100\,\mu m$  mesas of Ge and Si with optical lithography and reactive-ion etching using CF\_4 + O\_2. We then deposit 90 $\mu m \times$  90 $\mu m$  metal contacts pads of 500 Å/5000 Å Ti/Au by evaporation onto the mesas and use a standard lift-off technique. No contact annealing was performed.

All fabrication processes are carried out in a Class 100 clean room to avoid particulate contamination.

Electrical Measurements. I-V measurements were performed on a probe station using a Keithley 2400 Source Metering Unit. The current range of the measurement was -100 to +100 mA, limited by the compliancy of the instrument. To establish precision, the bias was swept back-and-forth 10 consecutive times with alternating polarity. The relative error was determined by dividing the standard deviation by the average of the measurements at a given point. ac conductance measurements were made using an Agilent 4284A Precision LCR Meter. The ac signal amplitude was 10 mV, and a dc bias across the device was swept from -10 to +10 V. The ac frequency was varied from 100 Hz to 1 MHz but held constant during each voltage sweep. The measured admittance was decomposed into conductance and susceptance. The conductance was essentially independent of frequency; however, the measurements are typically made at 10 kHz to reduce coupling with parasitic impedance.

The series resistance of a test device is estimated by measuring the slope of the dc I-V curve at high bias or by measurement using the ac impedance meter. The measured

complex impedance is decomposed into resistance and reactance components. The series resistance depends on the measurement instrument, method of connection, and current path, as this is a two-terminal measurement.

**Cross-Sectional Transmission Electron Microscopy (XTEM).** The XTEM samples were prepared by mechanical polishing and ion milling. The samples were initially thinned to  $8-10 \ \mu m \ via$  mechanical polishing and dimpling with diamond lapping films. The samples were further thinned with Ar<sup>+</sup> ion milling to make them electron transparent. The ion milling energies were progressively reduced (from 4 to 1 keV) to minimize the depth of the amorphous layer on the surface of the sample. The samples were characterized on a Philips CM200 TEM with a 200 keV operating voltage.

The twist angle between the Si NM and the Ge substrate was obtained by measuring the tilt angle between the (110) zone axis of the Si NM and the (130) zone axis of the Ge substrate. The twist angle was then extrapolated from knowledge of the actual angle between the (110) and (130) zone axes. Any miscut from the [001] direction of the surface of the Si NM or the Ge substrate was not accounted for in determining the approximate twist angle.

Acknowledgment. We thank G. Sun, Z. Q. Ma, and K. Turner for advice and S. Babcock for access to facilities. This research was primarily supported by AFOSR (Nanomembrane MURI, Grant No. FA9550-08-1-0337). The TEM and other structural characterizations (D.M.P. and A.M.C.) were supported by the DOE (Grant No. DE-FG02-03ER46028). A.M.K. is supported by a DoD SMART Scholarship, and D.M.P. is supported by an NSF Graduate Research Fellowship. We acknowledge facility support from NSF/MRSEC and from AFRL Hanscom.

### **REFERENCES AND NOTES**

- Demeester, P.; Pollentier, I.; De Dobbelaere, P.; Brys, C.; Van Daele, P. Epitaxial Lift-Off and Its Applications. Semicond. Sci. Technol. 1993, 8, 1124–1135.

- Chan, W. K.; Yablonovitch, E. In *Integrated Optoelectronics*; Dagenais, M., Leheny, R. F., Crow, J., Eds.; Academic Press: New York, 1995; pp 297–313.

- Jokerst, N. M.; Brooke, M. A.; Vendier, O.; Wilkinson, S.; Fike, S.; Lee, M.; Twyford, E.; Cross, J.; Buchanan, B.; Wills, S. Thin-Film Multimaterial Optoelectronic Integrated Circuits. *IEEE Trans. Compon., Packag., Manuf. Technol., Part B* **1996**, *19*, 97–106.

- Spearing, S. M. Materials Issues in Microelectromechanical Systems (MEMS). Acta Mater. 2000, 48, 179–196.

- Matthews, J. W.; Blakeslee, A. E. Defects in Epitaxial Multilayers. I. Misfit Dislocations. J. Cryst. Growth 1974, 27 118–125.

- Milnes, A. G.; Feucht, D. L. Heterojunctions and Metal-Semiconductor Junctions; Academic Press: New York, 1972.

- Kressel, H. Materials for Heterojunction Devices. Annu. Rev. Mater. Sci. 1980, 10, 287–309.

- Plössl, A.; Krauter, G. Wafer Direct Bonding: Tailoring Adhesion between Brittle Materials. *Mater. Sci. Eng., R* 1999, *R25*, 1–88.

- Slack, G. A.; Bartram, S. F. Thermal Expansion of Some Diamondlike Crystals. J. Appl. Phys. 1975, 46, 89–98.

- Sun, G.; Chang, F.; Soref, R. A. High Efficiency Thin-Film Crystalline Si/Ge Tandem Solar Cell. Opt. Express 2010, 18, 3746–3753.

- Zahler, J. M.; Ahn, C.; Zaghi, S.; Atwater, H. A.; Chu, C.; Iles, P. Ge Layer Transfer to Si for Photovoltaic Applications. *Proceedings of Symposium P on Thin Film Materials for Photovoltaics*; Materials Research Society: Warrendale, PA; 2001; Vol 681E, pp 63–68.

- Kanbe, H.; Komatsu, M.; Miyaji, M. Ge/Si Heterojunction Photodiodes Fabricated by Wafer Bonding. *Jpn. J. Appl. Phys.* 2006, 45, L644–L646.

- Colace, L.; Assanto, G. Germanium on Silicon for Near-Infrared Light Sensing. *IEEE Photonics J.* 2009, 1, 69–79.

- Sun, X.; Liu, J.; Kimerling, L. C.; Michel, J. Direct Gap Photoluminescence of n-Type Tensile-Strained Ge-on-Si. *Appl. Phys. Lett.* **2009**, *95*, 011911.

- Grenier, K.; Bordas, C.; Pinaud, S.; Salvagnac, L.; Dubuc, D. Germanium Resistors for RF MEMS Based Microsystems. *Microsyst. Technol.* 2008, 14, 601–606.

- Scott, S. A.; Lagally, M. G. Elastically Strain-Sharing Nanomembranes: Flexible and Transferable Strained Silicon and Silicon-Germanium Alloys. J. Phys. D 2007, 40, 75–92.

- Roberts, M. M.; Klein, L. J.; Savage, D. E.; Slinker, K. A.; Friesen, M.; Celler, G.; Eriksson, M. A.; Lagally, M. G. Elastically Relaxed Free-Standing Strained-Silicon Nanomembranes. *Nat. Mater.* 2006, *5*, 388–393.

- Huang, M.; Boons, C.; Roberts, M.; Savage, D. E.; Lagally, M. G.; Shaji, N.; Qin, H.; Blick, R.; Nairn, J. A.; Liu, F. Nanomechanical Architecture of Strained Bilayer Thin Films: From Design Principles to Experimental Fabrication. *Adv. Mater.* 2005, *17*, 2860–2864.

- Schmidt, O. G.; Deneke, C.; Manz, Y. M.; Muller, C. Semiconductor Tubes, Rods and Rings of Nanometer and Micrometer Dimension. *Physica E* 2002, *13*, 969–973.

- Kim, D.; Xiao, J.; Song, J.; Huang, Y.; Rogers, J. A. Stretchable, Curvilinear Electronics Based on Inorganic Materials. *Adv. Mater.* 2010, *22*, 2108–2124.

- Peng, W.; Roberts, M. M.; Nordberg, E. P.; Flack, F. S.; Colavita, P. E.; Hamers, R. J.; Savage, D. E.; Lagally, M. G.; Eriksson, M. A. Single-Crystal Silicon/Silicon Dioxide Multi-Layer Heterostructures Based on Nanomembrane Transfer. *Appl. Phys. Lett.* **2007**, *90*, 183107.

- Yuan, H.-C.; Wang, G.; Ma, Z.; Roberts, M. M.; Savage, D. E.; Lagally, M. G. Flexible Thin-Film Transistors on Biaxial- and Uniaxial-Strained Si and SiGe Membranes. *Semicond. Sci. Technol.* 2007, 22, 72–75.

- Freund, L. B.; Suresh, S. Thin Film Materials: Stress, Defect Formation and Surface Evolution; Cambridge University Press: Cambridge, U.K., 2006; pp 220–311.

- 24. Kopperschmidt, P.; Kästner., G.; Hesse, D.; Zakharov, N.; Gösele, U. High Bond Energy and Thermomechanical Stress in Silicon on Sapphire Wafer Bonding. *Appl. Phys. Lett.* **1997**, *70*, 2972–2974.

- Moutanabbir, O.; Gösele, U. Heterogeneous Integration of Compound Semiconductors. *Annu. Rev. Mater. Res.* 2010, 40, 469–500.

- Rouviere, J. L.; Rousseau, K.; Fournel, F.; Moriceau, H. Huge Differences Between Low- and High-Angle Twist Grain Boundaries: The Case of Ultrathin (001) Si Films Bonded to (001) Si Wafers. *Appl. Phys. Lett.* **2000**, *77*, 1135–1137.

- Sutton, A. P.; Balluffi, R. W. Interfaces in Crystalline Materials; Clarendon Press: Oxford, U.K., 1995; pp 70–110.

- Sagalowicz, L.; Rudra, A.; Syrbu, A.; Behrend, J.; Salomonsson, F.; Streubel, K.; Hammar, M.; Bentell, J. Structure of the Wafer Fused InP (001)-GaAs (001) Interface. *Philos. Mag. Lett.* **1997**, *76*, 445–452.

- Phillpot, S. R.; Wolf, D. Grain Boundaries in Silicon from Zero Temperature through Melting. J. Am. Ceram. Soc. 1990, 73, 933–937.

- Otsuki, A. Energies of (001) Twist Grain Boundaries in Silicon. Acta Mater. 2001, 49, 1737–1745.

- Silvestri, H. H.; Bracht, H.; Hansen, J. L.; Larsen, A. N.; Haller, E. E. Diffusion of Silicon in Crystalline Germanium. *Semi*cond. Sci. Technol. 2006, 21, 758–762.

- Bengtsson, S.; Engstrom, O. Interface Charge Control of Directly Bonded Silicon Structures. J. Appl. Phys. 1989, 66, 1231–1239.

- Ki, Y. B.; Ferain, I.; Fleming, P.; Morris, M.; Goorsky, M.; Colinge, C. Low Temperature Germanium to Silicon Direct Wafer Bonding Using Free Radical Exposure. *Appl. Phys. Lett.* 2010, *96*, 102110.

- Kanbe, H.; Hirose, M.; Ito, T.; Taniwaki, M. Crystallographic Properties of Ge/Si Heterojunctions Fabricated by Wet Wafer Bonding. J. Electron. Mater. 2010, 39, 1248–1255.

- Shewchun, J.; Temple, V. A. K. Theoretical Tunneling Current Characteristics of the SIS (Semiconductor-Insulator-Semiconductor) Diode. J. Appl. Phys. 1972, 43, 5051– 5061.

- Sze, S. M.; Ng, K. K. Physics of Semiconductor Devices, 3rd ed.; John Wiley & Sons: Hoboken, NJ, 2007; pp 417–463.

VOL.5 • NO.2 • 1179-1189 • 2011

1188

- Leipold, W. C.; Feuchtwang, T. E. Theoretical Considerations of Band-Structure Determination from Tunneling in Thin-Film Heterojunctions. *Phys. Rev. B.* **1974**, *10*, 2195– 2204.

- Kim, T.; Carlson, A.; Ahn, J.; Sang, M. W.; Wang, S.; Huang, Y.; Rogers, J. A. Kinetically Controlled, Adhesiveless Transfer Printing Using Microstructured Stamps. *Appl. Phys. Lett.* 2009, *94*, 113502.

- Schroder, D. K. Semiconductor Material and Device Characterization, 3rd ed.; John Wiley & Sons: Hoboken, NJ, 2006; pp 17, 146–149.

- Satta, A.; Simoen, E.; Janssens, T.; Clarysse, T.; De Jaeger, B.; Benedetti, A.; Hoflijk, I.; Brijs, B.; Meuris, M.; Vandervorst, W. Shallow Junction Ion Implantation in Ge and Associated Defect Control. *J. Electrochem. Soc.* **2006**, *153*, G229– G233.

- Sun, S.; Sun, Y.; Liu, Z.; Lee, D.; Peterson, S.; Pianetta, P. Surface Termination and Roughness of Ge(100) Cleaned by HF and HCl Solutions. *Appl. Phys. Lett.* **2006**, *88*, 1–3.

- Kim, J.; McVittie, J.; Saraswat, K.; Nishi, Y. Passivation Studies of Germanium Surfaces. *Solid State Phenom.* 2008, 134, 33–36.